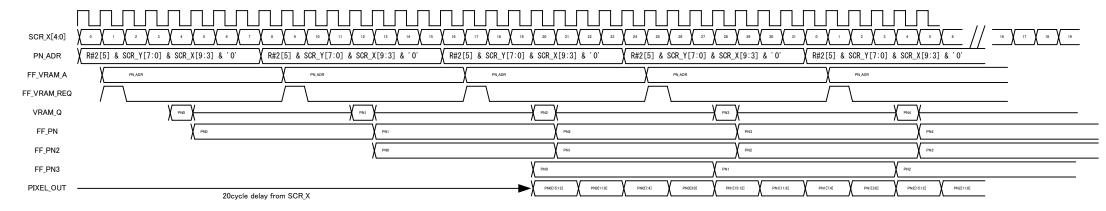

TH9958 GRAPHIC6 timing chart

Copyright (C)2008 t.hara

このモードは、基本的に GRAPHIC5 と同じだが、2bit/pixel の GRAPHIC5 に対し、4bit/pixel になるため、VRAMを16bit幅(倍幅)で読み出すことで処理している。

要するに読み出し幅が違うだけでタイミングは GRAPHIC5 と全く同じである。

(1)pattern name table のアドレス決定

VRAM address の 17bit は、それぞれ次の値になる。

ADR[ 16] = R#2 [5] ADR[15: 8] = SCR\_Y[7:0] ADR[ 7: 1] = SCR\_X[9:3]

※2byteずつ読み出すので、ADR[0]=0 と ADR[0]=1 の 2byteペアを一度に読み出す。

本物の VDP は、8bit幅64KBの DRAM を2つ接続することで 16bit幅64KB を実現している。

そのうち片方しか装備していない場合に VRAM 64KB として動作できるように GRAPHIC5以前のモードは

8bitアクセスしている。

そのような特殊なモード切替を実施しているために、GRAPHIC5以前と GRAPHIC6,7 では VRAM の物理的な配列が異なっている。

常に 16bit幅アクセスした方がDRAMバンド幅効率は良いが、GRAPHIC5以前のモードを 16bit幅でアクセスするモードは搭載されていないようだ。

→ TH9958 では GRAPHIC5以前のモードで 16bit幅アクセスによる高速動作モードも用意する