作成したボードの動作確認のために、テストベンチマークソフトを作成しました。

ソースのみをアーカイブしてあります。AKI-H8/3048Fに付属のアセンブラ用です。

| lcdtest.asm |

単純に液晶へ表示するテスト。うまく動けば「LCD Test ... Ok」と表示されます。 |

| sramtest.asm |

SRAM の接続を確認するプログラム。うまく動けば液晶に「SRAM A-BUS TestOk」と表示されます。 |

| sramtest2.asm |

SRAM-IC の動作を確認するプログラム。終了までは 34分ほどかかります。 |

sramtest.asm には lcdtest.asm の内容が全て含まれています。

sramtest2.asm には sramtest.asm の内容が全て含まれています。

sramtest.asm は、SRAM上の1つのアドレスに 0〜255 の値を書き込んで、即座

に読み込み一致することを確認します。これが失敗すると「SRAM D-BUS Test」

のところでエラーになるわけですが、エラーになるケースは、

・SRAMのデータバスの接続がおかしい場合

・/WEまたは/CSに異常がある場合

・SRAM-ICが正常に動作していない場合(物理的に破損、電源周り等)

等です。

アドレスバスの設定値が 1bit のみ異なる2つのアドレスに対して、異なる値を書

き込み、正常に読めることを確認します。/WE, /CS は接続されていて、/OE が

未接続の状態だと、最後に書き込んだ値が読み出せてしまうようなので、この

テストはパスしてしまいます。ただしその場合、次のテストで検出されます。

これが失敗すると「SRAM A-BUS Test」のところでエラーになるわけですが、

エラーになるケースは、

・SRAMのアドレスバスの接続がおかしい場合

・/WEまたは/OE,/CSの接続に異常がある場合

・SRAM-ICが正常に動作していない場合(物理的に破損、電源周り等)

等です。

エラー時には、エラー情報として値を表示します(意味はソースを見てください (^^;)。

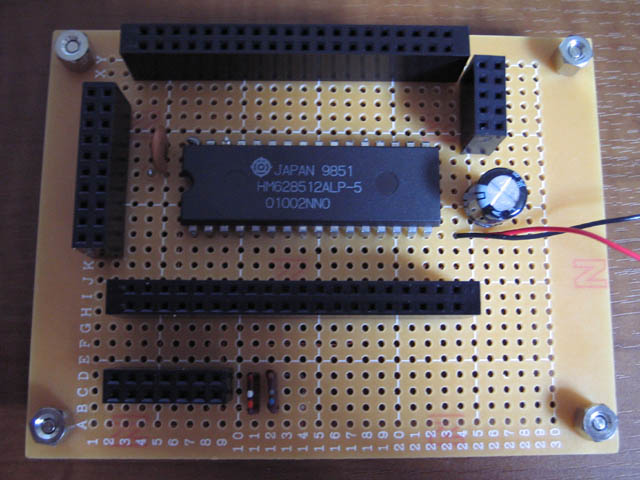

SRAM-IC は、以前失敗した工作から無理矢理引きはがしたモノ(ICソケット使っ

てませんでした)なので、破損してる可能性もあり、念のため全てのアドレスにつ

いて 0〜255 の値を書き込んで読み出せる確認を行いました。

サブルーチン Wait4ms は、本当に 4ms の待ちなのかは怪しいところです。ちゃんと

計算してません。アセンブラのサンプルプログラムのルーチンをそのまま持ってきて

ます (^^;

早速、作成したボードでテストベンチを動かしてみるとエラーが発生。

よく見ると、CN3 の内側の接続が、すべて1pinずつずれてました。実体配線図まで

作って確認していたのですが、その図の段階でずれていました (^_^;

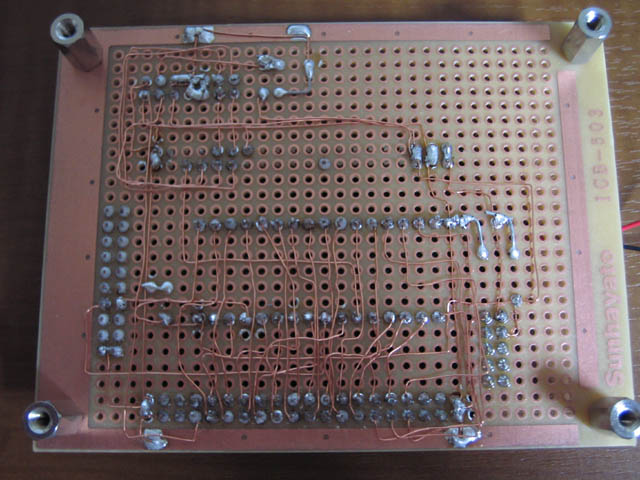

幸いなことに、ボードは破損しなかったので、接続し直して、テスタで念入りに接続

確認して、再度チェック。配線の修正がしやすいように、最短距離ではなくハンダ付

け部分を避けるように配線したために、端が配線の束になり、非常に引っかかりや

すく危険。意外と被覆が溶けにくいのはわかっていたので、思い切って直線距離に

配線し直し。ついでに、電源安定用のコンデンサと、電源スイッチを追加。

迂回配線をやめただけでだいぶスッキリしました。

今度はテストを問題なく通過しました。

sramtest.asm では、sramの初期化を行ってますが、ウェイトについてはデフォルト

(3state)のままです。私が使ったSRAM-IC なら、ノーウェイトでも動きそうな気が

しますが・・・必要に応じて調整してください (^_^;

配線:

SRAM の A0〜A18 を、H8/3048F の A0〜A18(Port1,2,5) へ直結。

SRAM の D0〜7 を、H8/3048F の D8〜D15(Port3) へ直結。

SRAM の /OE を、H8/3048F の /RD へ直結。

SRAM の /WE を、H8/3048F の /HWR へ直結。

SRAM の /CS を、H8/3048F の /CS1(Port8) へ直結。

あとは、SRAM に電源供給して 0.1uF 程度のパスコンをかましてます。

液晶は、AKI-H8/3048Fのマザーボードと同じビット並びで、PortA に接続します。

H8/3048F は モード6で動かすため、AKI-H8/3048F の CN5 の 1-2ピンをショート

させた状態で使います。モード6は、16MB のアドレス空間を持ち、それを8等分した

領域(1つ2MB)それぞれに対して /CS0〜7 の信号が出ています。

/CS0 は 0x000000〜, /CS1 は 0x200000〜, /CS2 は 0x400000〜 という対応で、

そこにアクセスするときだけ Lレベルになります。

今回は、/CS1 を SRAM の /CS (ChipSelect) に接続したので、SRAM は 0x200000〜

0x3FFFFF の時だけ有効になります。しかし、512KB の SRAM なので、0x280000

以降は 0x200000からの 512KBの繰り返しになります。

ただ接続するだけなので難易度は低いですが、甘く見て導通テストなどを怠るとは

まります (^_^;;;

メモリマップ

メモリマップを見ての通り、/CS0 に対応するブロックは内蔵ROMが、/CS7 に対応する

ブロックは内蔵RAMと内蔵I/Oレジスタが存在しているため、重複しない /CS1 を選択

しました。といっても、512KBなら 2MBのブロック内に4つ現れるので、一部が内蔵メモリ

と重複していても、全てのアドレスにアクセスできます。しかし、H8/3052 や H8/3069

などに交換した場合や、搭載する SRAM の容量を増やす場合によけいなことを考えな

くて済むのは、やはり /CS1〜/CS6 でしょう。

未接続のアドレスが多数ありますが、そこにはアクセスしてはいけません。

SRAMのミラーが現れるのは、A19, A20 が未接続だからです。

AKI-H8/3048FのCPUボードは232Cのレベル変換も行ってくれるので、CN4に出て

いる信号を DSUB9pinに接続すれば、PCと通信できるはずです。

起動直後に通信待ちになり、232C経由でアプリが送られてきたら、SRAMにロードし

て実行するようなファームウェアを作れば、いちいちボードから外して ROM更新して

また戻すという面倒な作業をしなくて済みますし、100回前後という更新回数制限も

おそれる必要が無くなります。次回は、それに挑戦です。

[前へ][▲上へ][次へ]